Son el corazón de la electrónica digital. Básicamente, todas las compuertas lógicas tienen una salida y dos entradas, algunas compuertas lógicas como la compuerta NOT o el inversor tienen solo una entrada y una salida. Las entradas de las compuertas lógicas están diseñadas para recibir solo datos binarios (bajo 0 o alto 1) al recibir la señal de voltaje.

El nivel lógico en bajo representa cero volts y el nivel lógico en alto representa 3 o 5 volts.

Es posible conectar cualquier número de compuertas lógicas para diseñar un circuito digital requerido. Prácticamente, implementamos una gran cantidad de compuertas lógicas en circuitos integrados, mediante las cuales podemos guardar el espacio físico ocupado por éstas. También es posible realizar operaciones complicadas a altas velocidades mediante el uso de circuitos integrados (IC).

Combinando compuertas lógicas, podemos diseñar muchos circuitos específicos, como flip flops, multiplexores, registros de desplazamiento, etc.

Niveles lógicos digitales

Un nivel lógico se define como un estado o voltaje específico de una señal, sabemos que 0 y 1 son los dos estados de compuertas lógicas. Los niveles lógicos 0 y 1 se conocen como BAJO y ALTO, respectivamente. En electrónica digital, estos niveles lógicos binarios desempeñan un papel crucial en el almacenamiento y la transferencia de datos.

En general, estos niveles lógicos se pueden entender como estados de encendido y apagado. Como se mencionó anteriormente, los niveles lógicos se introducen en la compuerta lógica mediante el voltaje de suministro.

De manera similar, si el voltaje de suministro a la compuerta lógica es de 5 voltios o 3,3 voltios (para circuitos integrados modernos), se refiere al nivel lógico alto o estado de encendido. Los fabricantes seguirán el TTL (Transistor – Transistor Logic) como nivel de voltaje estándar, mientras diseñan los circuitos integrados.

¿Qué es activo alto y activo bajo?

El pin bajo activo debe estar conectado a un nivel lógico bajo o a tierra. De la misma manera, el pin alto activo debe estar conectado a un nivel lógico alto como pudiera ser 5 voltios o 3.3 voltios.

Comprendamos esto de una manera simple. Cuando vemos el pin de habilitación CE en un IC de registro de desplazamiento, sin ninguna línea (barra), lo conectamos a una entrada activa baja, es decir, a 0 voltios de tierra. De lo contrario, si vemos el pin de habilitación con una línea como (CE) ̅, lo conectamos a la entrada alta activa, es decir, a 3,3 o 5 voltios de suministro, para habilitar el pin.

Niveles Lógicos TTL

Los transistores son interruptores controlados eléctricamente. Los niveles de voltaje de las familias lógicas son

- VOH – mín. nivel de voltaje de salida para señal ALTA

- VOL – max. Nivel de voltaje de salida para señal BAJA

- VIH – min. nivel de voltaje de entrada de un dispositivo para ser considerado en señal ALTA

- VIL – max. Nivel de voltaje de entrada de un dispositivo para ser considerado en señal BAJA

Si observamos los niveles lógicos TTL, podemos identificar que el nivel mínimo de alto voltaje para la salida es de 2.7 voltios. Esto significa que, cuando el dispositivo está funcionando en ALTO, el voltaje debe ser de al menos 2,7 voltios.

De manera similar, el nivel del estado alto tendrá un voltaje mínimo para la entrada, el cual es de 2 voltios. Por lo tanto, los voltajes superiores a 2 voltios se considerarán como lógicos 1, en un dispositivo TTL. Los voltajes entre 0,8 voltios y 2 voltios se conocen como margen de ruido.

De manera similar, el nivel máximo de estado bajo tendrá un voltaje para la entrada, el cual es de 0,8 voltios.

Por ello, los voltajes menores a 0 voltios se considerarán como lógicos 0, en un dispositivo TTL. Entonces, cuando el dispositivo lógico recibe voltajes entre 0.8 V y 2 V, el nivel lógico del dispositivo cambiará entre Alto y Bajo. Este cambio se llama ‘Flotante’.

Niveles lógicos CMOS

Los dispositivos lógicos CMOS también se conocen como dispositivos de 3,3 voltios debido a que tendrán el nivel máximo de voltaje de 3,3 V. Esta es una tecnología avanzada que ejecutará los dispositivos con bajo suministro de energía (3,3 V en lugar de 5 V).

Sobre todo, utilizamos dispositivos de 5 V (compatibles con TTL) para diseñar compuertas lógicas, por lo que estos dispositivos CMOS se utilizan para interactuar con dispositivos TTL. Un dispositivo CMOS puede interactuar con cualquier dispositivo TTL y no requieren ningún componente adicional.

Por ejemplo, el valor mínimo para un nivel lógico alto (1) de un dispositivo CMOS es de 2,4 V. Por lo tanto, este dispositivo se puede interpretar con un dispositivo TTL que tiene una tensión de entrada mínima lógica en estado 1 como 2 V.

Pero, antes de conectar los dispositivos TTL a CMOS (3.3 V y 5 V), debemos verificar que los dispositivos de 3.3 V sean o no tolerantes a 5 V. Debido a que muchos de ellos causarán daños en el chip permanentemente cuando suministremos voltajes superiores a 3.6 V. Podemos utilizar un circuito divisor de voltaje o palancas de nivel lógico para controlar las señales de voltaje de 5 V.

Margen de ruido

El margen de ruido de un nivel lógico se define como la brecha de voltaje entre la baja tensión máxima de entrada alta (VIL máx.) y la tensión máxima de la entrada baja (VIL mín.) de una compuerta lógica. El margen de ruido también se define como la cantidad por la cual la señal de voltaje excede el nivel de umbral para el mínimo o alto exacto.

Vamos a entender esto claramente con un ejemplo. Cuando un circuito lógico está alterando entre 0 voltios y 1.2 voltios, con cualquier voltaje por debajo de 0.2 voltios se considera BAJO, es decir, 0. Y cualquier voltaje superior a 1 voltio se considera ALTO, es decir, 1.

Los dispositivos lógicos CMOS tienen mayor nivel de ruido o margen de ruido que los dispositivos lógicos TTL porque su tensión de salida mínima para alta lógica (VOH min) está más cerca de la tensión de alimentación y la tensión máxima de salida para baja lógica (VOL máx.) es aproximadamente 0. Por lo tanto, este nivel es la cantidad máxima de ruido que un circuito lógico puede soportar.

Si aplicamos un voltaje de cierto nivel de ruido, no sabemos con certeza si el circuito responderá o no. El nivel de ruido es el nivel de voltaje no deseado, causado por interferencia externa tal como fluctuaciones de voltaje de suministro y otros conductores en el circuito.

El nivel de ruido que puede tolerar un circuito se denomina “Inmunidad al ruido” o “Margen de ruido“. Para dispositivos TTL, el rango de tolerancia de los voltajes de salida es mayor que el de los voltajes de entrada.

Tipos de Compuertas Logicas

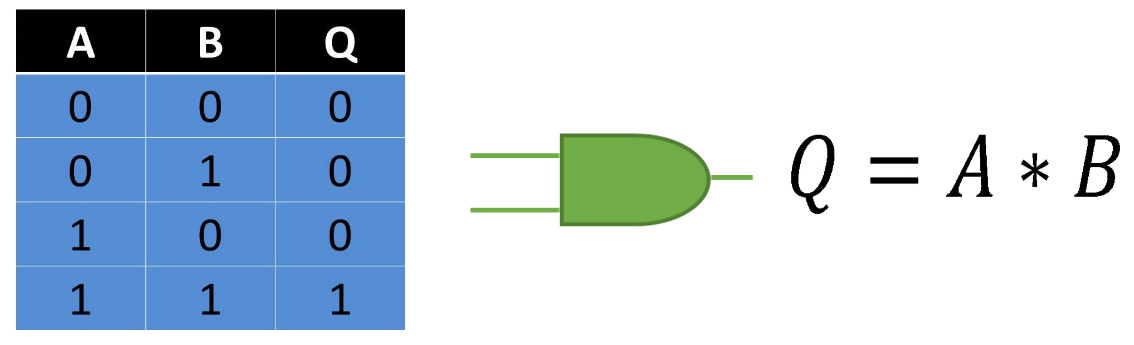

Compuerta AND

Esta compuerta es representada por una multiplicación en el Algrebra de boole. Indica que es necesario que en todas sus entradas se tenga un estado binario 1 para que la salida otorgue un 1 binario. En caso contrario de que falte alguna de sus entradas con este estado o no tenga si quiera una accionada, la salida no podrá cambiar de estado y permanecerá en 0. Esta puede ser simbolizada por dos o más interruptores en serie de los cuales todos deben estar activos para que esta permita el flujo de la corriente.

Fig. 2 Tabla, Representación y Fórmula Compuerta AND.

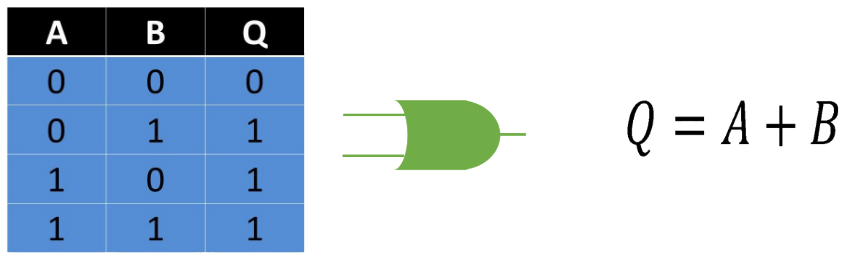

Compuerta OR

En el Algebra de Boole esta es una suma. Esta compuerta permite que con cualquiera de sus entradas que este en estado binario 1, su salida pasara a un estado 1 también. No es necesario que todas sus entradas estén accionadas para conseguir un estado 1 a la salida pero tampoco causa algún inconveniente. Para lograr un estado 0 a la salida, todas sus entradas deben estar en el mismo valor de 0. Se puede interpretar como dos interruptores en paralelo, que sin importar cual se accione, será posible el paso de la corriente.

Fig. 3 Tabla, Representación y Fórmula Compuerta OR.

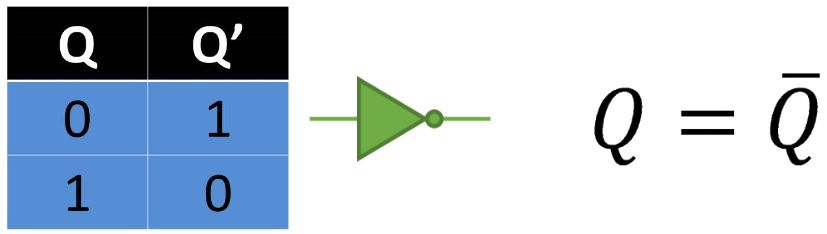

Compuerta NOT

En este caso esta compuerta solo tiene una entrada y una salida y esta actúa como un inversor. Para esta situación en la entrada se colocara un 1 y en la salida otorgara un 0 y en el caso contrario esta recibirá un 0 y mostrara un 1. Por lo cual todo lo que llegue a su entrada, será inverso en su salida.

Fig. 4 Tabla, Representación y Fórmula Compuerta NOT.

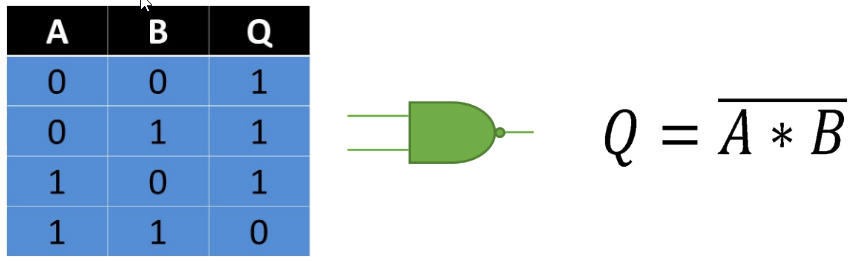

Compuerta NAND

También denominada como AND negada, esta compuerta trabaja al contrario de una AND ya que al no tener entradas en 1 o solamente alguna de ellas, esta concede un 1 en su salida, pero si esta tiene todas sus entradas en 1 la salida se presenta con un 0.

Fig. 5 Tabla, Representación y Fórmula Compuerta NAND.

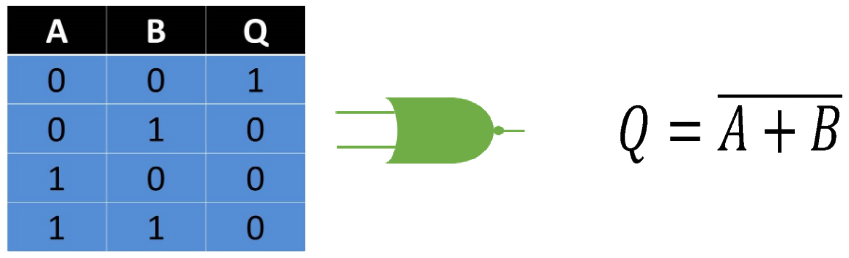

Compuerta NOR

Así como vimos anteriormente, la compuerta OR también tiene su versión inversa. Esta compuerta cuando tiene sus entradas en estado 0 su salida estará en 1, pero si alguna de sus entradas pasa a un estado 1 sin importar en qué posición, su salida será un estado 0.

Fig. 6 Tabla, Representación y Fórmula Compuerta NOR.

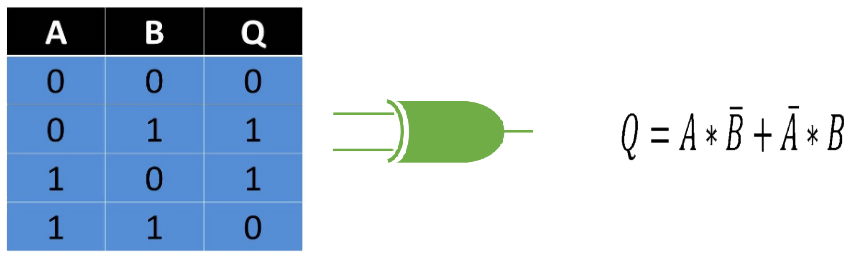

Compuerta XOR

También llamada OR exclusiva, esta actúa como una suma binaria de un digito cada uno y el resultado de la suma seria la salida. Otra manera de verlo es que con valores de entrada igual el estado de salida es 0 y con valores de entrada diferente, la salida será 1.

Fig. 7 Tabla, Representación y Fórmula Compuerta XOR.

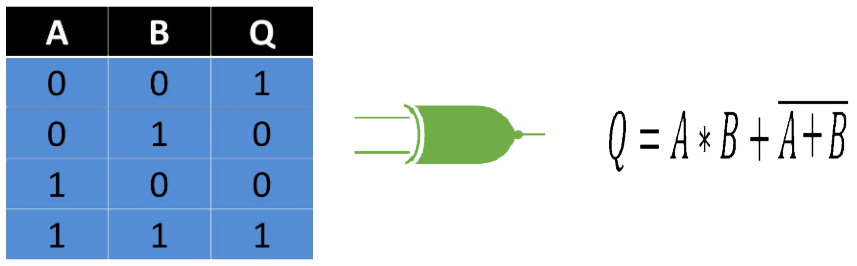

Compuerta XNOR

Esta es todo lo contrario a la compuerta XOR, ya que cuando las entradas sean iguales se presentara una salida en estado 1 y si son diferentes la salida será un estado 0.

Fig. 8 Tabla, Representación y Fórmula Compuerta XNOR.

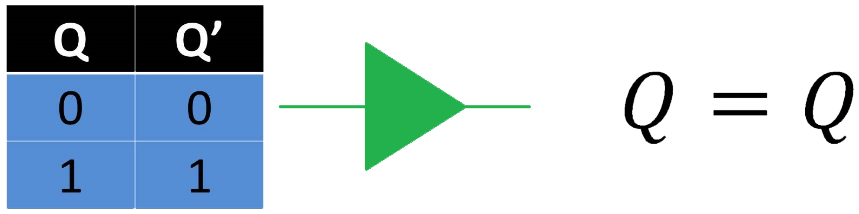

Compuerta IF

Esta compuerta no es una muy utilizada o reconocida ya que su funcionamiento en estados lógicos es parecido a si solo hubiera un cable conectado porque exactamente lo que se le coloque en la entrada, se encontrara en la salida. Pero también es conocido como un buffer, en la práctica se utiliza como amplificador de corriente o como seguidor de tensión para adaptar impedancias.